# PXI

**NI-Sync User Manual**

November 2003 Edition Part Number 370926A-01

#### Worldwide Technical Support and Product Information

ni.com

#### National Instruments Corporate Headquarters

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100

#### **Worldwide Offices**

Australia 1800 300 800, Austria 43 0 662 45 79 90 0, Belgium 32 0 2 757 00 20, Brazil 55 11 3262 3599, Canada (Calgary) 403 274 9391, Canada (Ottawa) 613 233 5949, Canada (Québec) 450 510 3055, Canada (Toronto) 905 785 0085, Canada (Vancouver) 514 685 7530, China 86 21 6555 7838, Czech Republic 420 224 235 774, Denmark 45 45 76 26 00, Finland 385 0 9 725 725 11, France 33 0 1 48 14 24 24, Germany 49 0 89 741 31 30, Greece 30 2 10 42 96 427, India 91 80 51190000, Israel 972 0 3 6393737, Italy 39 02 413091, Japan 81 3 5472 2970, Korea 82 02 3451 3400, Malaysia 603 9131 0918, Mexico 001 800 010 0793, Netherlands 31 0 348 433 466, New Zealand 0800 553 322, Norway 47 0 66 90 76 60, Poland 48 22 3390150, Portugal 351 210 311 210, Russia 7 095 783 68 51, Singapore 65 6226 5886, Slovenia 386 3 425 4200, South Africa 27 0 11 805 8197, Spain 34 91 640 0085, Sweden 46 0 8 587 895 00, Switzerland 41 56 200 51 51, Taiwan 886 2 2528 7227, Thailand 662 992 7519, United Kingdom 44 0 1635 523545

For further support information, refer to the *Technical Support and Professional Services* appendix. To comment on the documentation, send email to techpubs@ni.com.

© 2003 National Instruments Corporation. All rights reserved.

## **Important Information**

#### Warranty

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this document is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### Trademarks

$CVI^{TM}$ ,  $IVI^{TM}$ , LabVIEW<sup>TM</sup>, MXI<sup>TM</sup>, National Instruments<sup>TM</sup>, NI<sup>TM</sup>, ni.com<sup>TM</sup>, NI-DAQ<sup>TM</sup>, NI-FGEN<sup>TM</sup>, NI-Motion<sup>TM</sup>, NI-VISA<sup>TM</sup>, NI-VXI<sup>TM</sup>, and RTSI<sup>TM</sup> are trademarks of National Instruments Corporation.

Product and company names mentioned herein are trademarks or trade names of their respective companies.

#### Patents

For patents covering National Instruments products, refer to the appropriate location: **Help**»**Patents** in your software, the patents.txt file on your CD, or ni.com/patents.

#### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

(1) NATIONAL INSTRUMENTS PRODUCTS ARE NOT DESIGNED WITH COMPONENTS AND TESTING FOR A LEVEL OF RELIABILITY SUITABLE FOR USE IN OR IN CONNECTION WITH SURGICAL IMPLANTS OR AS CRITICAL COMPONENTS IN ANY LIFE SUPPORT SYSTEMS WHOSE FAILURE TO PERFORM CAN REASONABLY BE EXPECTED TO CAUSE SIGNIFICANT INJURY TO A HUMAN.

(2) IN ANY APPLICATION, INCLUDING THE ABOVE, RELIABILITY OF OPERATION OF THE SOFTWARE PRODUCTS CAN BE IMPAIRED BY ADVERSE FACTORS, INCLUDING BUT NOT LIMITED TO FLUCTUATIONS IN ELECTRICAL POWER SUPPLY, COMPUTER HARDWARE MALFUNCTIONS, COMPUTER OPERATING SYSTEM SOFTWARE FITNESS, FITNESS OF COMPILERS AND DEVELOPMENT SOFTWARE USED TO DEVELOP AN APPLICATION, INSTALLATION ERRORS, SOFTWARE AND HARDWARE COMPATIBILITY PROBLEMS, MALFUNCTIONS OR FAILURES OF ELECTRONIC MONITORING OR CONTROL DEVICES, TRANSIENT FAILURES OF ELECTRONIC SYSTEMS (HARDWARE AND/OR SOFTWARE), UNANTICIPATED USES OR MISUSES, OR ERRORS ON THE PART OF THE USER OR APPLICATIONS DESIGNER (ADVERSE FACTORS SUCH AS THESE ARE HEREAFTER COLLECTIVELY TERMED "SYSTEM FAILURES"). ANY APPLICATION WHERE A SYSTEM FAILURE WOULD CREATE A RISK OF HARM TO PROPERTY OR PERSONS (INCLUDING THE RISK OF BODILY INJURY AND DEATH) SHOULD NOT BE RELIANT SOLELY UPON ONE FORM OF ELECTRONIC SYSTEM DUE TO THE RISK OF SYSTEM FAILURE. TO A VOID DAMAGE, INJURY, OR DEATH, THE USER OR APPLICATION DESIGNER MUST TAKE REASONABLY PRUDENT STEPS TO PROTECT AGAINST SYSTEM FAILURES, INCLUDING BUT NOT LIMITED TO BACK-UP OR SHUT DOWN MECHANISMS. BECAUSE EACH END-USER SYSTEM IS CUSTOMIZED AND DIFFERS FROM NATIONAL INSTRUMENTS' TESTING PLATFORMS AND BECAUSE A USER OR APPLICATION DESIGNER MAY USE NATIONAL INSTRUMENTS' PRODUCTS IN COMBINATION WITH OTHER PRODUCTS IN A MANNER NOT EVALUATED OR CONTEMPLATED BY NATIONAL INSTRUMENTS, THE USER OR APPLICATION DESIGNER NAY USE NATIONAL INSTRUMENTS PRODUCTS IN COMBINATION WITH OTHER PRODUCTS IN A MANNER NOT EVALUATED OR CONTEMPLATED BY NATIONAL INSTRUMENTS, THE USER OR APPLICATION DESIGNER NAY USE NATIONAL INSTRUMENTS PRODUCTS ARE INCORPORATED IN A SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN, PROCESS AND SAFETY LEVEL OF SUCH SYSTEM FOR DUCTS ARE INCORPORATED IN A SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN, PROCESS AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

## **About This Manual**

| Conventions           | xi  |

|-----------------------|-----|

| Related Documentation | xii |

## Chapter 1 Introduction, Installation, and Configuration

| About the NI-Sync Driver Software                     | 1-1 |

|-------------------------------------------------------|-----|

| Introduction                                          |     |

| Operating System Support                              | 1-2 |

| Application Software and Programming Language Support | 1-2 |

| Device Support                                        | 1-2 |

| Installing the Software                               | 1-2 |

| Device and System Configuration                       | 1-3 |

| Using Measurement & Automation Explorer               | 1-3 |

| Identifying Your PXI System                           | 1-3 |

| Locating Your NI PXI-665x Modules                     | 1-3 |

## Chapter 2 Building and Programming Applications

| The NI-Sync Instrument Driver                             | 2-1 |

|-----------------------------------------------------------|-----|

| Creating a Windows Application Using LabVIEW              |     |

| Developing an NI-Sync Application                         |     |

| Example Programs                                          |     |

| Creating a Windows Application Using LabWindows/CVI       | 2-2 |

| Developing an NI-Sync Application                         | 2-2 |

| Example Programs                                          |     |

| Creating a Windows Application Using Microsoft Visual C++ | 2-2 |

| Developing an NI-Sync Application                         | 2-3 |

| Example Programs                                          | 2-3 |

| Special Considerations                                    | 2-3 |

| NI-Sync Programming Flow                                  |     |

| Initialize                                                |     |

| Configure Hardware                                        | 2-5 |

| Accessing Attributes                                      |     |

| Connect Terminals                                         |     |

| Clock Terminals                                           | 2-6 |

| Trigger Terminals                                         |     |

| Software Trigger Terminals                                | 2-8 |

| Configure and Perform Measurement   | 2-8  |

|-------------------------------------|------|

| Disconnect Terminals                | 2-9  |

| Clock Terminals                     | 2-9  |

| Trigger Terminals                   | 2-9  |

| Software Trigger Terminals          |      |

| Close                               | 2-10 |

| Utility                             | 2-10 |

| Terminal Connection Information     | 2-11 |

| Instrument Driver Utility Functions | 2-11 |

| Advanced                            | 2-12 |

| Frequency Measurement               | 2-12 |

| FPGA Reconfiguration                |      |

| -                                   |      |

## Chapter 3 Synchronizing Multiple NI PXI-4472 Modules

| Theory of Operation: Synchronizing Data Acquisition Across Multiple  |      |

|----------------------------------------------------------------------|------|

| NI PXI-4472 Modules                                                  | 3-1  |

| Synchronizing Signals for Multiple NI PXI-4472 Modules in a          |      |

| Single Chassis                                                       | 3-2  |

| Delta-Sigma ADCs and the Oversample Clock                            | 3-2  |

| The NI PXI-4472 SYNC Pulse                                           | 3-4  |

| The Acquisition Start Trigger                                        | 3-6  |

| Using the NI PXI-665x to Route Synchronization Signals Between       |      |

| Multiple Chassis                                                     | 3-7  |

| Sharing the Oversample Clock Between Chassis                         | 3-7  |

| Sharing the SYNC Pulse Between Chassis                               | 3-9  |

| Sharing the Acquisition Start Trigger Between Chassis                | 3-10 |

| Configuring the Chassis                                              | 3-13 |

| Configuration #1: One Chassis with Synchronized Acquisition          |      |

| and One CPU                                                          | 3-14 |

| LabVIEW                                                              | 3-14 |

| LabWindows/CVI                                                       | 3-14 |

| What You Need to Get Started                                         | 3-15 |

| Connecting the NI PXI-665x Device                                    | 3-15 |

| Connecting the NI PXI-4472 Devices                                   | 3-15 |

| Configuring and Running the Software Example                         |      |

| Using the niSync_DSA Example Single Chassis VI                       | 3-16 |

| Using the niSync_DSA Example 1 Chassis [Low Level] VI                | 3-17 |

| Using niSync_DSA_Example Single Chassis                              |      |

| (LabWindows/CVI Example Project)                                     | 3-17 |

| Configuration #2: Two or Three Chassis with Synchronized Acquisition |      |

| and One CPU                                                          | 3-18 |

| LabVIEW                                                              | 3-18 |

| LabWindows/CVI                                                       |

|----------------------------------------------------------------------|

| What You Need to Get Started                                         |

| Connecting the MXI-3 Devices                                         |

| Connecting the NI PXI-665 <i>x</i> Devices                           |

| Connecting the NI PXI-4472 Devices                                   |

| Configuring and Running the Software Example                         |

| Using the niSync_DSA_Example 2 or 3 Chassis Finite Acq VI            |

| and the niSync_DSA_Example 2 or 3 Chassis Continuous                 |

| Acq VI                                                               |

| Using the niSync_DSA Example 2 Chassis [Low Level] VI                |

| Using niSync_DSA_Example Dual Chassis Finite and                     |

| niSync_DSA_Example Dual Chassis Continuous Acq                       |

| (LabWindows/CVI Example Projects)3-25                                |

| Using niSync_DSA_Example Dual Chassis Finite GUI                     |

| (LabWindows/CVI Example Project)3-26                                 |

| Configuration #3: Four or More Chassis with Synchronized Acquisition |

| and One CPU                                                          |

| What You Need to Get Started3-27                                     |

| Connecting the MXI-3 Devices                                         |

| Connecting the NI PXI-665x                                           |

| Connecting the NI PXI-4472 Devices                                   |

| Configuring and Running the Software Example                         |

| Using the niSync_DSA_Example N Chassis VI3-31                        |

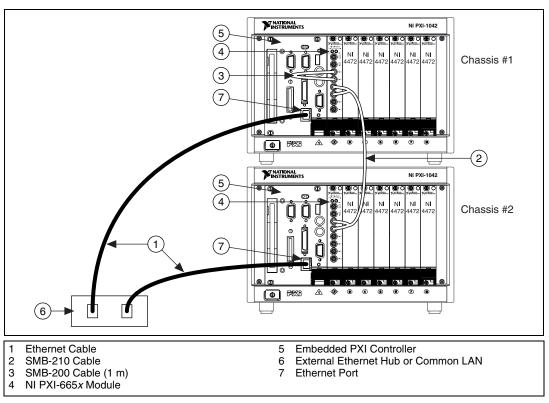

| Configuration #4: Two Chassis with Synchronized Acquisition          |

| and Two CPUs                                                         |

| What You Need to Get Started                                         |

| Connecting to Ethernet                                               |

| Connecting the NI PXI-665 <i>x</i>                                   |

| Connecting the NI PXI-4472 Modules                                   |

| Configuring and Running the Software Example                         |

| Running the Multi-CPU DSA Examples Programs                          |

## Chapter 4 Synchronizing Multiple NI PXI-5112 Modules

| NI PXI-5112 Theory of Operation                                        | 4-1 |

|------------------------------------------------------------------------|-----|

| Using the NI PXI-665 <i>x</i> to Route Synchronization Signals Between |     |

| Multiple Chassis                                                       | 4-2 |

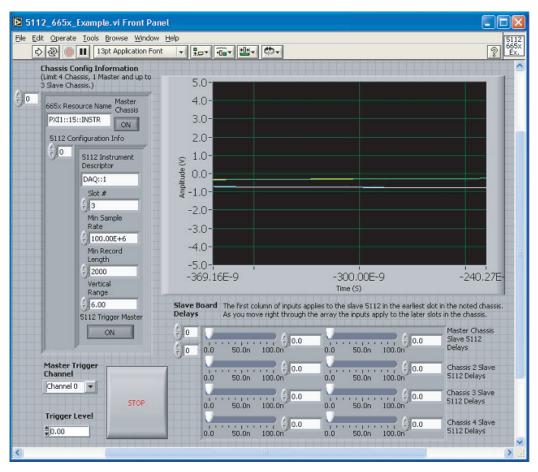

| Example Overview                                                       | 4-2 |

| What You Need to Get Started                                           | 4-4 |

| Setting Up a Multichassis PXI System                                   | 4-4 |

| Connecting the NI PXI-665x Devices                                     | 4-5 |

| Connecting the NI PXI-5112 Devices                                     | 4-6 |

| Configuring and Running the Software Example                           | 4-6 |

| Example Functionality                         | 4-7  |

|-----------------------------------------------|------|

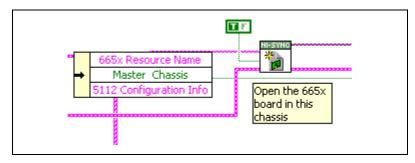

| Initialization and Error Checking             | 4-7  |

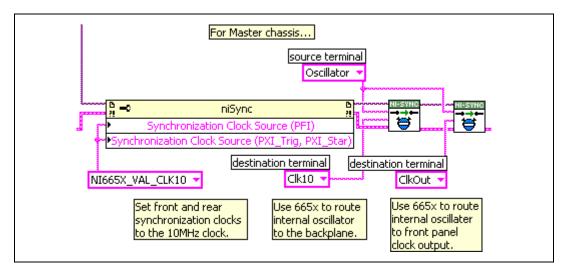

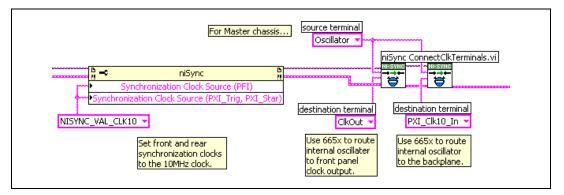

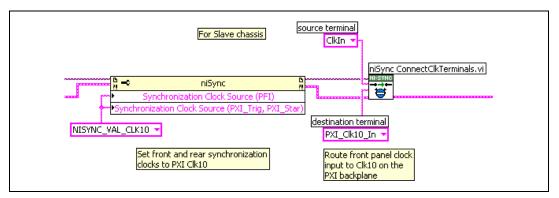

| Configuring the 10 MHz Timebase               | 4-8  |

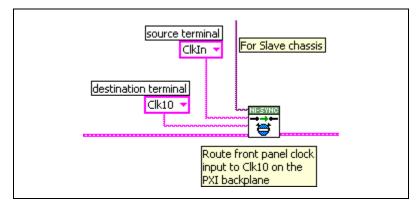

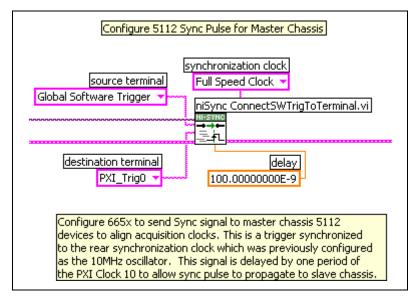

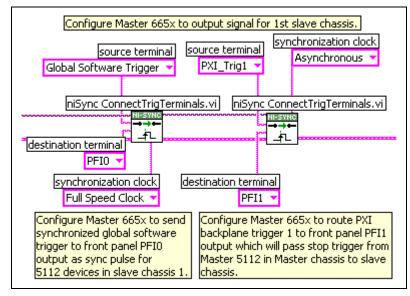

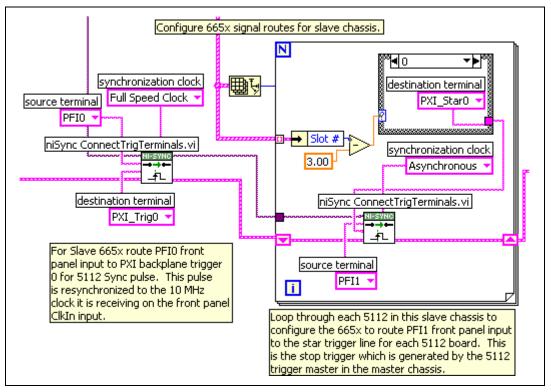

| Routing the Necessary Synchronization Signals | 4-10 |

| Configuring the NI PXI-5112 Synchronization   |      |

| and Acquisitions                              | 4-13 |

| Beginning the Acquisition                     | 4-14 |

| Closing and Error Checking                    | 4-15 |

## Chapter 5 Synchronizing Multiple NI PXI-6115 Modules

| Using the NI PXI-665x to Route Synchronization Signals Between<br>Multiple Chassis |

|------------------------------------------------------------------------------------|

| Multiple Chassis                                                                   |

|                                                                                    |

| Example Overview                                                                   |

| What You Need to Get Started 5-3                                                   |

| Setting Up the Multichassis PXI System                                             |

| Connecting the NI PXI-665x Devices                                                 |

| Connecting the NI PXI-6115 Devices                                                 |

| Configuring and Running the Software Example                                       |

| Example Functionality                                                              |

| Initialization and Error Checking5-6                                               |

| Configuring the NI PXI-665x Clocks                                                 |

| Routing the Necessary Synchronization Signals                                      |

| Configuring the NI PXI-6115 Synchronization                                        |

| and Acquisitions5-13                                                               |

| Beginning the Acquisition5-13                                                      |

| Closing and Error Checking 5-13                                                    |

## Chapter 6 Synchronizing Multiple NI MIO Modules

| Theory of Operation                                            |  |

|----------------------------------------------------------------|--|

| Using the NI PXI-665x to Route Synchronization Signals Between |  |

| Multiple Chassis                                               |  |

| Example Overview                                               |  |

| What You Need to Get Started                                   |  |

| Setting Up the Multichassis PXI System                         |  |

| Connecting the NI PXI-665x Devices                             |  |

| Connecting the MIO Devices                                     |  |

| Configuring and Running the Software Example                   |  |

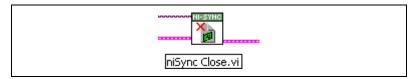

| Example Functionality                                | 6-6 |

|------------------------------------------------------|-----|

| Initialization and Error Checking                    | 6-6 |

| Configuring the Scan Clock                           | 6-7 |

| Routing the Necessary Synchronization Signals        | 6-7 |

| Configuring the MIO Synchronization and Acquisitions | 6-8 |

| Beginning the Acquisition                            | 6-9 |

| Closing and Error Checking                           | 6-9 |

## Chapter 7 Synchronizing Multiple NI PXI-5411 Modules

| NI PXI-5411 Theory of Operation                                | 7-1 |

|----------------------------------------------------------------|-----|

| Using the NI PXI-665x to Route Synchronization Signals Between |     |

| Multiple Chassis                                               | 7-2 |

| Example Overview                                               |     |

| What You Need to Get Started                                   | 7-3 |

| Setting Up the Multichassis PXI System                         | 7-4 |

| Connecting the NI PXI-665x Devices                             |     |

| Connecting the NI PXI-5411 Devices                             |     |

| Configuring and Running the Software Example                   |     |

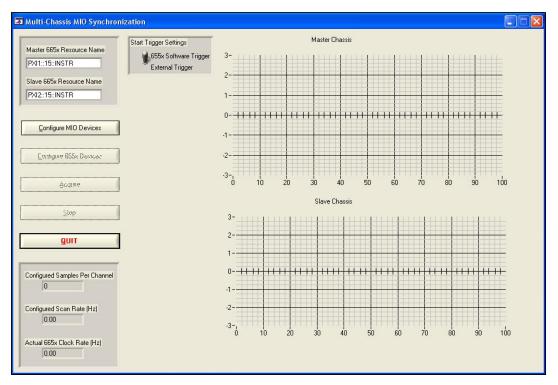

| Example Functionality                                          | 7-8 |

| Initialization and Error Checking                              |     |

| Configuring the 10 MHz Timebase                                |     |

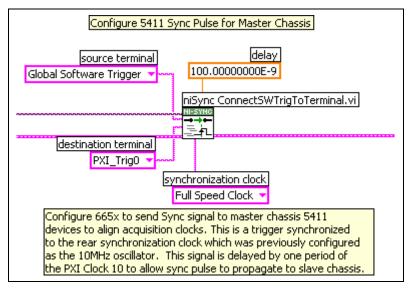

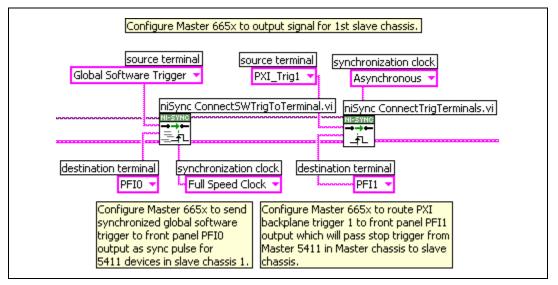

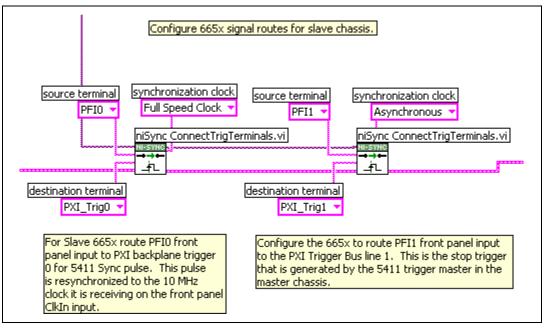

| Routing the Necessary Synchronization Signals                  |     |

| Configuring the NI PXI-5411 Synchronization and Generations    |     |

| Beginning the Signal Generation                                |     |

| Closing and Error Checking                                     |     |

| - •                                                            |     |

## Appendix A Technical Support and Professional Services

## Glossary

## Index

The *NI-Sync User Manual* is for users of the NI-Sync driver software, an application programming interface (API) for controlling NI PXI-665*x* timing modules. This manual describes the fundamentals of developing applications with NI-Sync. In addition, this manual includes examples for using NI-Sync with specific measurement hardware.

## Conventions

|           | The following conventions appear in this manual:                                                                                                                                                                                                                                                                                                                    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <>        | Angle brackets that contain numbers separated by an ellipsis represent a range of values associated with a bit or signal name—for example, DIO<30>.                                                                                                                                                                                                                 |

| »         | The » symbol leads you through nested menu items and dialog box options to a final action. The sequence <b>File</b> » <b>Page Setup</b> » <b>Options</b> directs you to pull down the <b>File</b> menu, select the <b>Page Setup</b> item, and select <b>Options</b> from the last dialog box.                                                                      |

| •         | The $\blacklozenge$ symbol indicates that the following text applies only to a specific product, a specific operating system, or a specific software version.                                                                                                                                                                                                       |

|           | This icon denotes a note, which alerts you to important information.                                                                                                                                                                                                                                                                                                |

| <u>_</u>  | This icon denotes a caution, which advises you of precautions to take to avoid injury, data loss, or a system crash.                                                                                                                                                                                                                                                |

| bold      | Bold text denotes items that you must select or click in the software, such as menu items and dialog box options. Bold text also denotes parameter names.                                                                                                                                                                                                           |

| italic    | Italic text denotes variables, emphasis, a cross reference, or an introduction<br>to a key concept. This font also denotes text that is a placeholder for a word<br>or value that you must supply.                                                                                                                                                                  |

| monospace | Text in this font denotes text or characters that you should enter from the keyboard, sections of code, programming examples, and syntax examples. This font is also used for the proper names of disk drives, paths, directories, programs, subprograms, subroutines, device names, functions, operations, variables, filenames and extensions, and code excerpts. |

## **Related Documentation**

The following documents contain information that you might find helpful as you read this manual:

- *PICMG 2.0 R3.0, CompactPCI Core Specification*, available from PICMG, available from www.picmg.org

- PXI Specification, Revision 2.1, available from www.pxisa.org

- NI PXI-665x User Manual, available from ni.com/manuals

- Getting Started with Multi-Chassis Synchronization Using the NI PXI-665x, available from ni.com/manuals

# Introduction, Installation, and Configuration

This chapter provides an overview of the NI-Sync driver software and explains how to install and configure NI-Sync for use with NI PXI-665x timing modules.

## About the NI-Sync Driver Software

NI-Sync is a library of VIs and functions for controlling NI PXI-665*x* timing modules. Using NI-Sync, you can configure all aspects of timing and synchronization for NI PXI-665*x* devices, including sharing trigger signals and clocks in one or more chassis. You can use NI-Sync in conjunction with other measurements software, such as NI-DAQmx or Traditional NI-DAQ, to create advanced, high-channel-count measurements that span multiple PXI chassis.

## Introduction

The NI-Sync driver software includes the following:

- NI-Sync instrument driver API and device driver

- Hardware-specific example software, illustrating multichassis synchronization for the following measurement devices:

- NI PXI-4472 modules

- NI PXI-5112 modules

- NI PXI-6115/6120 modules

- NI PXI-5411 modules

When developing your application, refer to Chapter 2, *Building and Programming Applications*, for information about creating an application with your specific application development environment (ADE). Also, refer to the appropriate hardware-specific chapter in this manual for specific examples of using NI-Sync with your application.

## **Operating System Support**

NI-Sync supports Windows 2000/XP and LabVIEW RT.

#### Application Software and Programming Language Support

Table 1-1 lists the application software versions that NI-Sync supports. If you are not using National Instruments application software, refer to Table 1-2.

| NI Application Software                     | Versions NI-Sync Supports |

|---------------------------------------------|---------------------------|

| LabVIEW                                     | 6.1 or later              |

| LabVIEW RT Module                           | 7.0 or later              |

| LabWindows <sup>TM</sup> /CVI <sup>TM</sup> | 5.5 or later              |

Table 1-1.

National Instruments Application Software Support

Table 1-2 lists additional programming languages supported by NI-Sync.

| Table 1-2. | Additional | Programming | Language Support |

|------------|------------|-------------|------------------|

|------------|------------|-------------|------------------|

| Programming Language | Versions NI-Sync Supports |

|----------------------|---------------------------|

| ANSI C               | ✓                         |

| Microsoft Visual C++ | 5.0 or later              |

#### **Device Support**

NI-Sync supports the NI PXI-665x family of timing modules.

## Installing the Software

The software package that ships with the NI PXI-665x provides the following items:

- NI-Sync driver software

- LabVIEW example code

- LabWindows/CVI example code

- NI PXI-665x User Manual

Complete the following steps to install your NI-Sync software:

- 1. Insert the NI-Sync CD into the CD-ROM drive of your computer.

- 2. Run the Setup.exe program to install the NI-Sync software on your system.

Several high-level examples are provided to give you a starting point in using the NI PXI-665*x* to synchronize data acquisition across multiple PXI chassis with various National Instruments PXI modules.

Note Be sure to install the NI-Sync software *before* installing the NI PXI-665x hardware.

## **Device and System Configuration**

Before you begin using your NI PXI-665*x* timing module, you must ensure that your PXI system software is configured properly. NI-Sync uses PXI configuration information to enable features such as chassis identification, slot identification, and trigger terminal reservation. This configuration information is enabled by identifying PXI system components in Measurement & Automation Explorer.

## **Using Measurement & Automation Explorer**

Measurement & Automation Explorer (MAX) is a Windows-based application that you use to configure and view National Instruments device settings under Windows operating systems.

## **Identifying Your PXI System**

Double-click the **Measurement & Automation Explorer** icon on your desktop to run MAX. In the Configuration pane, select **My System» Devices and Interfaces»PXI System**. Using the PXI System view, you can identify the controller and chassis in your PXI system. Refer to the PXI System context help for detailed instructions on identifying your PXI system components.

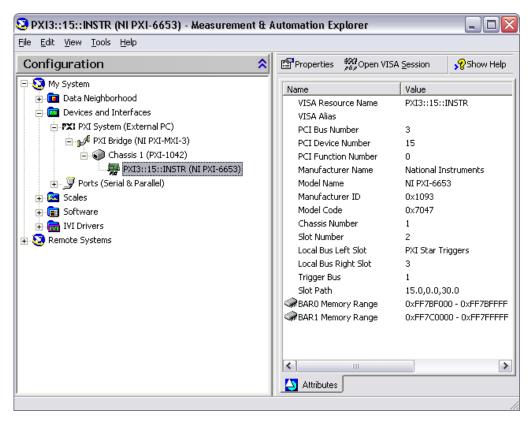

## Locating Your NI PXI-665x Modules

Once you have identified your PXI system components, you can locate your NI PXI-665*x* modules by browsing the PXI System view (**My System»Devices and Interfaces»PXI System**). Instances of the NI PXI-665*x* timing module are displayed under their corresponding chassis. By selecting an instance of the NI PXI-665x, you can view its attributes, including VISA Resource Name and PXI slot number. Refer to Figure 1-1 for an example of the type of device information available in MAX.

**Note** Viewing NI PXI-665*x* device information in MAX is useful for obtaining the VISA Resource Name for an instance of the NI PXI-665*x*. The VISA Resource Name is used to create a session to a device using the NI-Sync API. Refer to Chapter 2, *Building and Programming Applications*, for detailed information about device initialization.

Figure 1-1. NI PXI-665*x* Device Information in MAX

## Building and Programming Applications

This chapter describes the fundamentals of building and programming NI-Sync applications for LabVIEW, LabWindows/CVI, and Microsoft Visual C++.

## **The NI-Sync Instrument Driver**

The NI-Sync driver software includes an instrument driver API for configuring attributes and programming the features of NI PXI-665x timing modules. The NI-Sync instrument driver function library is a C DLL. This DLL should be linked using the appropriate import library for your application development environment.

The following sections provide guidelines for creating applications that use the NI-Sync driver software.

**Note** If you are not using one of the tools listed, refer to your development tool reference manual for details on creating applications that call C DLLs.

## **Creating a Windows Application Using LabVIEW**

This section assumes that you are using LabVIEW 6.1 or later to manage your code development and that you are familiar with the LabVIEW environment basics.

## **Developing an NI-Sync Application**

To develop an NI-Sync application with LabVIEW, complete the following steps:

- 1. Open an existing or new LabVIEW VI.

- 2. From the Function Palette, locate the NI-Sync VIs at **Instrument I/O**» **Instrument Drivers**»NI-Sync.

- 3. Select the VIs you want to use and drop them on the block diagram to build your application.

## **Example Programs**

You can find LabVIEW example programs from the Windows **Start** menu at **Programs»National Instruments»NI-Sync»Examples**. The examples are organized by LabVIEW version number and measurement hardware.

## Creating a Windows Application Using LabWindows/CVI

This section assumes that you are using LabWindows/CVI 5.5 or later to manage your code development and that you are familiar with the LabWindows/CVI environment.

## **Developing an NI-Sync Application**

To develop an NI-Sync application with LabWindows/CVI, complete the following steps:

- 1. Open an existing or new project file.

- 2. Load the NI-Sync function panel at \VXIpnp\winnt\niSync.

- 3. Use the function panel to navigate the function hierarchy and generate function calls with the proper syntax and variable values.

#### **Example Programs**

You can find LabWindows/CVI example programs from the Windows **Start** menu at **Start»Programs»National Instruments» NI-Sync»Examples»CVI Examples**. The examples are organized by measurement hardware.

## Creating a Windows Application Using Microsoft Visual C++

This section assumes that you are using the Microsoft Visual C++ (MSVC) ADE to manage your code development and that you are familiar with the MSVC environment.

## **Developing an NI-Sync Application**

To develop an NI-Sync application with MSVC, complete the following steps:

- 1. Open an existing or new Visual C++ project to manage your application code.

- 2. Create files of type .c (C source code) or .cpp (C++ source code) and add them to the project. Make sure to include the NI-Sync header file in each source file:

#include "niSync.h"

- 3. Specify the directory that contains the NI-Sync header file under the Preprocessor»Additional include directories settings in your compiler. For MSVC 5.0/6.0, this setting is found under Project» Settings»C/C++. The NI-Sync header file is in the \VXIpnp\winnt\ include directory.

- 4. Add the NI-Sync import library niSync.lib to the project under the Link»General»Object/Library Modules setting. The NI-Sync import library is in the \VXIpnp\winnt\lib\msc folder.

- 5. Add NI-Sync function calls to your application.

- 6. Build your application.

## **Example Programs**

R

You can find C-based example programs from the Windows **Start** menu at **Start»Programs»National Instruments»NI-Sync»Examples»CVI Examples**. The examples are organized by measurement hardware.

**Note** While the C-based examples are written specifically for use with LabWindows/CVI, they can be adapted for use with MSVC and other C/C++ compilers.

## **Special Considerations**

When developing applications with MSVC, observe the following special considerations.

• **String Passing**—To pass strings as arguments to functions, pass a pointer to the first element of the character array. Be sure the string is null terminated.

## **NI-Sync Programming Flow**

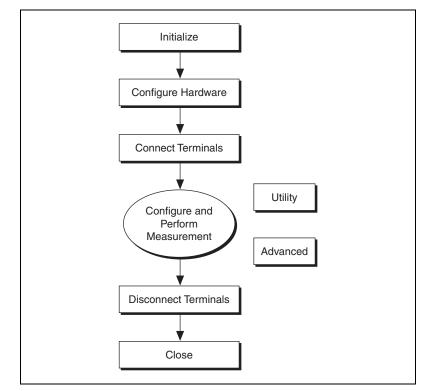

Figure 2-1 shows the basic programming flow of typical NI-Sync applications. NI-Sync VIs and functions are organized under the Initialize, Configure Hardware, Connect Terminals, Disconnect Terminals, and Close categories to assist you in understanding where you should call a function or VI in your applications. Functions and VIs that do not fall into the programming flow categories are considered Advanced or Utility functions that perform various tasks such as resetting the NI PXI-665*x* module, returning the revision number of the NI-Sync instrument driver and instrument firmware, and other functions.

Figure 2-1. Basic Programming Flow of an NI-Sync Application

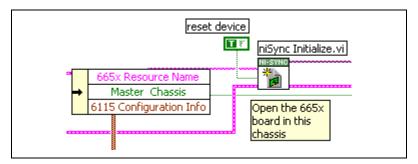

## Initialize

$\mathbb{N}$

For any application you write, you must first open a session to establish communication with the NI PXI-665x timing module using the **Initialize** VI or function.

| LabVIEW VI        | C Function  |

|-------------------|-------------|

| niSync Initialize | niSync_init |

In addition to establishing a session with the timing module, **niSync Initialize** can reset the device to a known state and verify that the NI-Sync instrument driver is valid for a particular instrument. The **Initialize** VI or function returns a ViSession handle you can use to identify the instrument in all subsequent NI-Sync calls.

**Note** The **Initialize** VI and function take the VISA Resource Name corresponding to an NI PXI-665*x* module and use this information to locate the instrument and create a session to it. You can obtain the VISA Resource Name for an instance of the NI PXI-665*x* using MAX. Refer to Chapter 1, *Introduction, Installation, and Configuration*, for an example of using MAX with the NI PXI-665*x*.

The **Initialize** VI and function create a new instrument session. Repeated calls to **Initialize** for the same resource name will return the same session. You can use this session in multiple program threads.

## **Configure Hardware**

Use Configuration VIs and functions to adjust settings of the timing and synchronization features of the NI PXI-665*x* module, including DAC input threshold voltage levels, DDS frequency, synchronization clock sources, and other settings and features needed for timing operations.

NI PXI-665*x* attributes are configured using a LabVIEW property node or the niSync\_SetAttribute and niSync\_GetAttribute functions.

## **Accessing Attributes**

In LabVIEW, you can find NI PXI-665*x* attributes in the **niSync** property node. To access these attributes, complete the following steps:

- 1. Open a VI.

- 2. Make sure you are viewing the block diagram. Navigate the **niSync** palette at **Instrument I/O**»**Instrument Drivers**»**NI-Sync** and drag the property node to the diagram.

- 3. Left-click the property node and select the attribute you want to use.

- 4. To configure additional attributes, resize the property node.

In C, attributes are accessed with the niSync\_SetAttribute... and niSync\_GetAttribute... functions. These functions correspond to a particular data type. For example, to set the PFI0 DAC voltage level (type ViReal64), use niSync\_SetAttributeViReal64.

Refer to the NI-Sync API Reference for a complete list of attributes.

#### **Connect Terminals**

After you have configured the NI PXI-665*x* timing module, you can route signals between terminals using the Connect Terminals functions. Connecting terminals forms the core of typical NI-Sync applications. Source and destination terminals can be connected using a variety of mechanisms. NI-Sync considers three types of terminals—clock terminals, trigger terminals, and software trigger terminals.

## **Clock Terminals**

Clock terminals include terminals associated with the 10 MHz PXI reference clock (PXI\_Clk10). Clock terminal connections are used to route clock signals between the backplane and front panel of the NI PXI-665*x* module. Refer to the *NI PXI-665x User Manual* for a complete discussion of clock terminals.

Clock terminal connections have a variety of uses, including:

- Multichassis PXI\_Clk10 synchronization

- PXI\_Clk10 replacement with a high-precision onboard oscillator

Clock terminal connections are characterized by source and destination terminals.

The following VI and function deal with clock terminal connections.

| LabVIEW VI                        | C Function                 |

|-----------------------------------|----------------------------|

| niSync Connect Clock<br>Terminals | niSync_ConnectClkTerminals |

## Trigger Terminals

Trigger terminals include terminals associated with hardware trigger lines. Trigger terminals can also carry clocks, but they are not associated with any specific clock signal. Trigger terminals include the PXI trigger lines (PXI\_Trig[0:7]), the PXI star triggers (PXI\_Star[0:12]), and the NI PXI-665x front panel PFI lines (PFI[0:5]). Refer to the *NI PXI-665x User Manual* for a complete discussion of trigger terminals.

You can use trigger terminals to route single digital pulses between chassis. In addition, trigger terminals can carry and distribute clock signals. Typical uses of trigger terminals include:

- Sharing a trigger signal to start data acquisition between multiple chassis

- Sharing a "sync pulse" to align common clocks on multiple chassis

- Distributing high-speed clock signals (typically on PXI\_Star terminals)

**Note** Some trigger types are reservable. That is, they can be connected to only a single source at a time. For example, PXI\_Trig terminals use TTL drivers and should not be driven by multiple signal sources. To solve this problem, NI driver software supports reservation of PXI\_Trig terminals so that only one source is active on a destination at any given time. This reservation software integrates with other NI measurements software to prevent multiple sources for a single PXI\_Trig terminal.

Trigger terminal connections are characterized by a source terminal, destination terminal, and synchronization clock. In addition, trigger terminal signals can be inverted or synchronized to the rising or falling edge of the specified synchronization clock. Trigger signals can also be routed asynchronously.

The following VI and function deal with trigger terminal connections.

| LabVIEW VI                          | C Function                  |

|-------------------------------------|-----------------------------|

| niSync Connect Trigger<br>Terminals | niSync_ConnectTrigTerminals |

$\mathbb{N}$

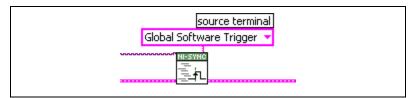

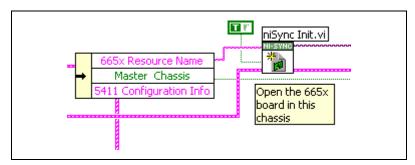

## Software Trigger Terminals

Software trigger terminals include those terminals associated with software-initiated trigger pulses. Currently, the NI PXI-665*x* timing module includes a single software trigger terminal, referred to as the Global Software Trigger. The Global Software Trigger terminal can be connected to any other trigger terminal (PXI\_Trig, PXI\_Star, and PFI). When the software trigger terminal is connected, a pulse can be sent to all connected destination terminals simultaneously.

Typical uses of the Global Software Trigger include:

- Generating a trigger signal to start data acquisition

- Generating a "sync pulse" to align common clocks on multiple chassis

- Resetting clocks (or divided clocks) to synchronize clock generation across multiple NI PXI-665*x* modules

Software trigger terminal connections are characterized by a source terminal (always set to the Global Software Trigger), a destination terminal (any valid trigger terminal destination), and a synchronization clock. In addition, the software trigger signal can be inverted, synchronized to the rising or falling edge of the specified synchronization clock, or delayed by an integer multiple of the synchronization clock period. Refer to the *NI PXI-665x User Manual* for a complete discussion of the Global Software Trigger.

The following VIs and functions deal with software trigger terminal connections.

| LabVIEW VIs                        | C Functions                    |

|------------------------------------|--------------------------------|

| niSync Connect Software<br>Trigger | niSync_ConnectSWTrigToTerminal |

| niSync Send Software<br>Trigger    | niSync_SendSoftwareTrigger     |

## **Configure and Perform Measurement**

After making terminal connections, you are ready to perform your measurement. Taking a measurement is an application-specific operation that typically involves the use of a Measurements API such as NI-DAQmx, Traditional NI-DAQ, NI-Scope, NI-FGEN, and so on. If you are synchronizing measurements using multiple NI PXI-4472, NI PXI-5112, NI PXI-6115/6120, or NI PXI-5411 modules, refer to the appropriate chapter of this manual for detailed examples of using your measurement device with NI-Sync.

**Note** If you are not using measurement devices discussed in this manual, refer to the reference manuals for your measurements hardware for specific instructions on configuring and performing a measurement.

## **Disconnect Terminals**

Once a measurement has been performed, connected terminals should be disconnected. This returns the PXI system to its premeasurement state and avoids disrupting the activity of other timing and synchronization applications. Terminals are disconnected by supplying the connected source and destination terminals to Disconnect VIs or functions.

Terminals are disconnected according to their type.

## **Clock Terminals**

Use the following VI or function to disconnect clock terminals.

| LabVIEW VI                           | C Function                    |

|--------------------------------------|-------------------------------|

| niSync Disconnect Clock<br>Terminals | niSync_DisconnectClkTerminals |

## **Trigger Terminals**

Use the following VI or function to disconnect trigger terminals.

| LabVIEW VI                             | C Function                     |

|----------------------------------------|--------------------------------|

| niSync Disconnect<br>Trigger Terminals | niSync_DisconnectTrigTerminals |

## **Software Trigger Terminals**

Use the following VI or function to disconnect software trigger terminals.

| LabVIEW VI                            | C Function                          |

|---------------------------------------|-------------------------------------|

| niSync Disconnect<br>Software Trigger | niSync_DisconnectSWTrigFromTerminal |

**Note** A special terminal value exists for disconnecting multiple terminals from a source or destination terminal. Use the AllConnected terminal (NISYNC\_VAL\_ALL\_CONNECTED) to disconnect multiple sources or destinations. If this value is supplied as the source and destination terminal, all connections of the specified terminal type are disconnected.

**Note** In addition to the explicit disconnect VIs and functions, you can use **niSync Reset** to disconnect all connected terminals.

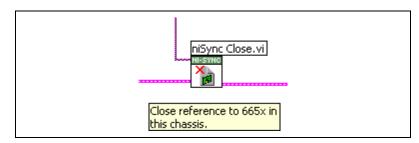

#### Close

When your program finishes, terminate the session with the **Close** VI or function.

| LabVIEW VI   | C Function   |

|--------------|--------------|

| niSync Close | niSync_close |

The **Close** VI or function is essential for deallocating memory and freeing other operating system resources. Every session you initialize must be closed, even if an error occurs during program execution.

While debugging your application, it is possible to abort the application without calling **Close**. While aborting execution should not cause problems, it is not recommended for terminating your application.

**Note** Calling **Close** will *not* disconnect terminals that were connected while a session is open. Terminals must be explicitly disconnected using Disconnect VIs/functions or by resetting the module.

## Utility

R

In addition to resource and terminal connection management, NI-Sync includes several Utility VIs and functions for performing tasks such as resetting the NI PXI-665*x*, converting error codes to messages, and obtaining information about existing terminal connections.

## **Terminal Connection Information**

NI-Sync includes VIs and functions for obtaining information about terminal connections.

| LabVIEW VIs                                       | C Functions                          |  |

|---------------------------------------------------|--------------------------------------|--|

| niSync Get Clock<br>Connection Info               | niSync_GetClkTerminalConnectionInfo  |  |

| niSync Get<br>Trigger<br>Connection Info          | niSync_GetTrigTerminalConnectionInfo |  |

| niSync Get<br>Software Trigger<br>Connection Info | niSync_GetSWTrigConnectionInfo       |  |

Using these VIs and functions, you can determine if a given destination terminal is connected. You also can determine the connection parameters, such as synchronization clock, clock edge, and signal inversion.

## **Instrument Driver Utility Functions**

In addition to terminal connection information, NI-Sync supports the standard set of instrument driver utility functions.

| LabVIEW VIs           | C Functions           |  |

|-----------------------|-----------------------|--|

| niSync Reset          | niSync_reset          |  |

| niSync Self-Test      | niSync_self_test      |  |

| niSync Revision Query | niSync_revision_query |  |

| niSync Error Message  | niSync_error_message  |  |

Refer to the NI-Sync API Reference for details regarding these functions.

## Advanced

NI-Sync also includes advanced features, including frequency measurement and FPGA reconfiguration.

## **Frequency Measurement**

NI-Sync can measure the frequency of a signal at the PFI0 terminal of an NI PXI-665x module. The following VI and function support this operation.

| LabVIEW VI               | C Function              |

|--------------------------|-------------------------|

| niSync Measure Frequency | niSync_MeasureFrequency |

Frequency measurement is useful for verifying that clock signals are properly connected. For example, a clock signal connected to PXI\_Star3 could be measured by connecting the PXI\_Star3 terminal to the PFI0 terminal and using the **Measure Frequency** VI or function.

## **FPGA Reconfiguration**

The NI PXI-665*x* module includes a field programmable gate array (FPGA) for managing the device's timing and synchronization features. For a detailed block diagram of the NI PXI-665*x*, refer to the *NI PXI-665x User Manual*. In some special cases, you may want to program the FPGA with an alternate bitstream file. The following VI and function support this operation.

| LabVIEW VI            | C Function           |  |

|-----------------------|----------------------|--|

| niSync Configure FPGA | niSync_ConfigureFPGA |  |

**Caution** FPGA Reconfiguration is a sensitive operation that can damage your NI PXI-665*x* module. Do *not* use this operation unless you are absolutely sure about what you are doing.

# 3

# Synchronizing Multiple NI PXI-4472 Modules

The NI PXI-665*x* Timing and Synchronization Module enables you to pass PXI timing and triggering signals between two or more PXI chassis. This module is especially useful for synchronizing acquisitions involving large numbers of NI PXI-4472 Dynamic Signal Acquisition modules. Tight multichassis synchronization guarantees simultaneous sampling and minimal interchannel phase mismatch in high-channel-count systems.

This chapter describes four typical hardware configurations where the NI PXI-665*x* enables synchronization for NI PXI-4472 Dynamic Signal Acquisition (DSA) modules in one or more PXI chassis. The necessary hardware, signal connections, and example code are described for each configuration.

NI highly recommends that you thoroughly review the *Theory of Operation: Synchronizing Data Acquisition Across Multiple NI PXI-4472 Modules* section before running the application examples or starting your application development. The main goal of this section is to familiarize you with the NI PXI-4472 synchronization signals and with how the NI PXI-665x hardware can extend this synchronization beyond a single PXI chassis. After familiarizing yourself with the concepts described here, move on to the LabVIEW or LabWindows/CVI example programs before beginning your software development.

The *NI PXI-665x User Manual*, NI PXI-4472 documentation, and remote chassis link (such as MXI-3) documentation might be useful to you as you read this document. You can download these documents from ni.com/manuals.

## Theory of Operation: Synchronizing Data Acquisition Across Multiple NI PXI-4472 Modules

The following sections provide low-level background information about the electrical signals needed to synchronize NI PXI-4472 modules. The *Synchronizing Signals for Multiple NI PXI-4472 Modules in a Single*  *Chassis* section describes the signals required to synchronize an acquisition when all NI PXI-4472 modules reside in the same PXI chassis. No NI PXI-665*x* is required in this case. The *Using the NI PXI-665x to Route Synchronization Signals Between Multiple Chassis* section discusses synchronization where NI PXI-4472 modules are physically located in two or more PXI chassis. In a multichassis system, two or more NI PXI-665*x* modules generate and route the necessary signals to synchronize all NI PXI-4472 channels in the system. The NI-Sync software package includes application examples that address three multichassis cases as well as a single-chassis case.

# Synchronizing Signals for Multiple NI PXI-4472 Modules in a Single Chassis

This section describes the synchronization between NI PXI-4472 modules housed in a single PXI chassis. This section introduces three signals: the oversample clock, the SYNC pulse, and the acquisition start trigger. The Using the NI PXI-665x to Route Synchronization Signals Between Multiple Chassis section frequently refers to these signals.

## **Delta-Sigma ADCs and the Oversample Clock**

The 24-bit A/D converters (ADCs) employed on the NI PXI-4472 belong to a class of components called *delta-sigma* (or  $\Delta\Sigma$ ) ADCs. The advantages of delta-sigma components as compared to other digitizers include high dynamic range, excellent linearity, and digital filtering to remove aliased frequency components from the data.

Most ADCs, including the successive approximation ADCs used in many data acquisition (DAQ) devices, are timed by a *sample clock*. This clock is simply a digital pulse train that drives the acquisition. In most cases, a rising edge on the sample clock signal starts a conversion. When an ADC is timed by a sample clock, the acquisition rate is equal to the frequency of the sample clock. For example, a 10 kHz sample clock produces a 10 kS/s acquisition rate.

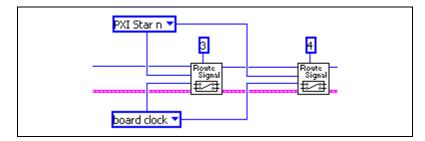

One distinguishing feature of delta-sigma converters, including those on the NI PXI-4472, is that they use an *oversample clock* to drive the conversion. As the name implies, the physical frequency of the oversample clock signal is greater than the sample rate. When a single NI PXI-4472 acquires data, the high-frequency oversample clock is locally generated by a Direct Digital Synthesis (DDS) chip on the device. If two or more NI PXI-4472 modules are run in a single PXI chassis, they must share the oversample clock to provide a tightly synchronized acquisition. When sharing this clock, one module becomes the "clock master," and the other modules become the "clock slaves." The clock master module must be placed in Slot 2 of the PXI chassis. The clock master uses the DDS chip to produce the oversample clock and drive its own acquisition. The clock master also exports the oversample clock to the PXI star trigger bus. Figure 3-1 shows a LabVIEW code snippet that illustrates how to export the oversample clock to a clock slave module in PXI Slots 3 and 4.

Figure 3-1. Exporting the Oversample Clock to PXI\_Star

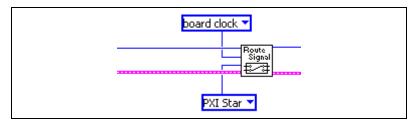

You now order each clock slave device to import the oversample clock from PXI\_Star to drive its ADCs. Figure 3-2 shows the LabVIEW code snippet for this operation.

Figure 3-2. Importing the Oversample Clock to Drive Slave ADCs

On the NI PXI-4472, the ratio between the oversample  $(f_{os})$  clock and the sample rate  $(f_s)$  can have one of two possible values, depending on the sample rate. Table 3-1 shows the possible values.

**Table 3-1.** Relationship Between the Sample Rate and Oversample Clock

| Sample Rate                 | Oversample Clock          |  |

|-----------------------------|---------------------------|--|

| $f_s \le 51.2 \text{ kS/s}$ | $f_{os} = 256 \times f_s$ |  |

| $f_s > 51.2 \text{ kS/s}$   | $f_{os} = 128 \times f_s$ |  |

The highest possible oversample frequency for the NI PXI-4472 occurs at either  $f_s = 51.2$  kS/s or  $f_s = 102.4$  kS/s. In both cases, the oversample rate is slightly faster than 13.1 MHz.

Most delta-sigma converters, including those on the NI PXI-4472, require a very steady frequency for the oversample clock. The DDS chip on the NI PXI-4472 has good frequency characteristics and fulfills this need. However, arbitrarily changing frequencies, such as those from tachometers, generally do not work well with delta-sigma ADCs. For this reason, the NI PXI-4472 and other National Instruments DSA products do not support external clocking from arbitrary signal sources. This constraint also applies when you use one or more NI PXI-665*x* modules for synchronization with NI PXI-4472 devices.

## The NI PXI-4472 SYNC Pulse

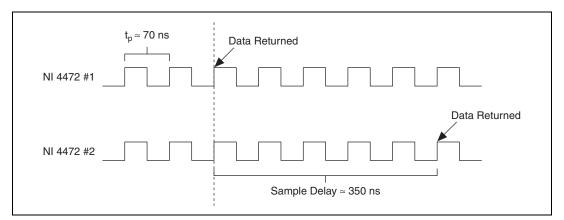

As discussed in the *Delta-Sigma ADCs and the Oversample Clock* section, the oversample clock is many times faster than the actual acquisition rate of the NI PXI-4472. Using the concepts described in that section, you can share the oversample clock between two or more NI PXI-4472 modules. This sharing guarantees that both modules sample at the same frequency and that there will be no drift between their acquisitions. However, oversample clock sharing does not guarantee that the samples on both modules are acquired at exactly the same time. Figure 3-3 illustrates the oversample pulse trains on two NI PXI-4472s sampling at 102.4 kS/s. In this example, there is a delay between acquisition samples of five oversample intervals, or about 350 ns. This delay may be any value up to a whole sample interval, which is about 10 µs at this acquisition rate.

Figure 3-3. Sample Delay Between NI PXI-4472 Modules After Receiving a Shared Oversample Clock

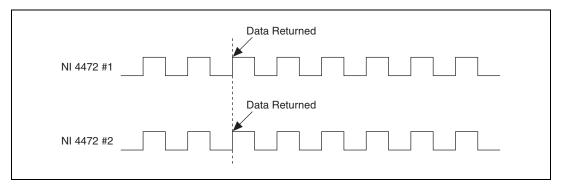

The solution to the clock-delay issue is to configure the master device to issue a SYNC pulse before the acquisition. The clock master sends a single active-low, or inverted, pulse on the PXI\_Trig5 line, the dedicated line for the SYNC pulse. The ADCs in the clock master and clock slaves receive this pulse nearly simultaneously. The SYNC pulse forces all the ADCs to a reset state, emptying their digital filters and synchronizing their clock dividers. After exiting the reset state, all NI PXI-4472 modules in the chassis run at the same frequency and have minimal phase difference between sample clocks. Figure 3-4 illustrates how this technique minimizes the sample delay.

Figure 3-4. NI PXI-4472 Modules with Shared Oversample Clock Using the SYNC Pulse

The NI PXI-4472 cannot acquire data while it is in the reset state that occurs immediately after it receives the SYNC pulse. During this period, the ADC returns only zeros. The length of the reset period  $T_{reset}$  (in samples) is a function of sample rate. Table 3-2 shows the possible lengths of the reset period.

| Table 3-2. | Reset Period | as a Function | of Sample Rate |

|------------|--------------|---------------|----------------|

|------------|--------------|---------------|----------------|

| Sample Rate                 | Reset Period (T <sub>reset</sub> ) |  |

|-----------------------------|------------------------------------|--|

| $f_s \le 51.2 \text{ kS/s}$ | $T_{reset} = 8,960$ samples        |  |

| $f_s > 51.2 \text{ kS/s}$   | $T_{reset} = 17,920$ samples       |  |

When all NI PXI-4472 modules are housed in a single chassis, the SYNC pulse is automatically handled by NI-DAQ, the NI driver software for DAQ hardware. Therefore, you do not need to make an explicit software call to generate or route the SYNC pulse. However, you must make specific calls to the NI PXI-665*x* modules in all chassis to properly generate and route the SYNC pulse when configuring a multichassis system. These calls are

discussed in the Using the NI PXI-665x to Route Synchronization Signals Between Multiple Chassis section.

## The Acquisition Start Trigger

After sharing the oversampling clock and issuing the SYNC pulse, the ADCs on every NI PXI-4472 in the system run in lock-step. At this point, the only remaining task is to synchronize the beginning of the data acquisition on each NI PXI-4472.

In the *Sharing the Oversample Clock Between Chassis* and *Sharing the SYNC Pulse Between Chassis* sections, clock master and clock slave modules were discussed. Because the oversample clock is carried on the PXI star trigger lines, the clock master module must always reside in Slot 2. This concept of master and slave devices is also useful when discussing the acquisition start trigger. Exactly one module should be the "trigger master," while all the other NI PXI-4472 modules are "trigger slaves." However, the trigger master can reside in any PXI slot; it is not limited to Slot 2. Therefore, the clock master and trigger master are not necessarily the same module.

First, configure all trigger slave NI PXI-4472 modules to start their acquisitions on a digital trigger from a PXI\_Trig line. You can choose PXI\_Trig<0..4> for the start trigger; the choice of PXI\_Trig0 line for this example is arbitrary. Figure 3-5 shows how to wire a trigger cluster to the **AI Start** VI to accomplish this task.

Figure 3-5. Starting the Acquisition on a Trigger Slave

Next, direct the trigger master to export a pulse to PXI\_Trig0 when it begins acquiring. This pulse, in turn, triggers all the slaves. Figure 3-6 shows the LabVIEW code snippet used to configure the trigger master.

Figure 3-6. Routing the Start Trigger and Starting the Acquisition on the Trigger Master

The code in Figure 3-6 uses immediate software triggering for the trigger master NI PXI-4472. However, you could easily change the triggering parameters on the trigger master **AI Start** VI to use external digital or analog triggering.

# Using the NI PXI-665*x* to Route Synchronization Signals Between Multiple Chassis

The Synchronizing Signals for Multiple NI PXI-4472 Modules in a Single Chassis section discussed why the oversample clock, SYNC pulse, and acquisition start trigger are necessary and addressed the software calls needed to share these signals between NI PXI-4472 modules residing in a single PXI chassis. This section explains how the NI PXI-665x enables you to expand the channel count of your system by sharing these same three signals among multiple chassis.

## Sharing the Oversample Clock Between Chassis

In a single-chassis synchronized DSA system, the clock master NI PXI-4472 generates the oversample clock and distributes it to the clock slave modules. When the DSA system consists of multiple PXI chassis, the NI PXI-665*x* in the master chassis generates the oversample clock and distributes it to all the NI PXI-4472 modules. Thus, every DSA device in a multichassis system is a clock slave; you do not define a clock master NI PXI-4472.

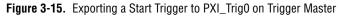

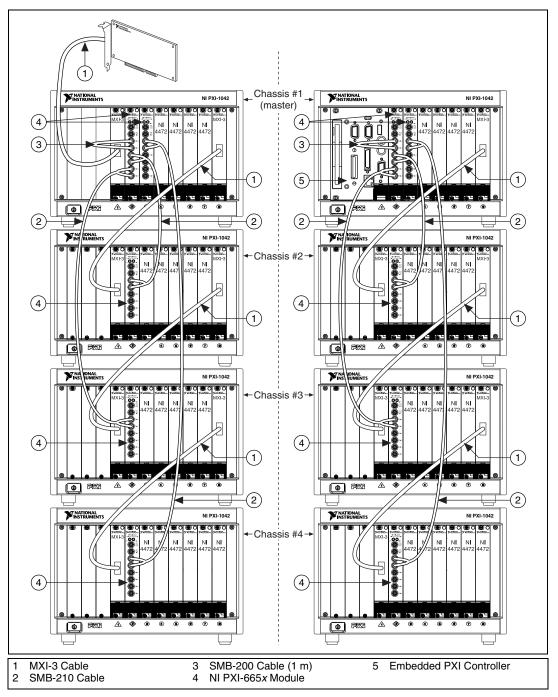

First, consider a system with either two or three chassis where each chassis contains an NI PXI-665x in Slot 2 and several NI PXI-4472 modules. One NI PXI-665x is defined as the "NI PXI-665x master." This module uses its DDS chip to generate the appropriate oversample clock. The NI PXI-665x master is also responsible for distributing the oversample clock to all the other "slave" chassis. Each NI PXI-665x (both master and slave) must route the oversample clock to the PXI backplane so that it can drive the ADCs on the NI PXI-4472 modules housed in the chassis. Refer to Figure 3-17 for an illustration of the hardware setup for this configuration.

In this diagram, the NI PXI-665*x* in the top chassis is the master, while the NI PXI-665*x* modules in the other two chassis are slaves. The master connects to both slaves. Notice that the master includes one cable that "loops back" to itself. This loopback guarantees that the oversample pulse train travels over a similar path before reaching the PXI star trigger bus on both backplanes. As the pulse travels along the coaxial cable and through the circuitry on the NI PXI-665*x*, it creates a significant propagation delay. The loopback minimizes this timing difference and ensures symmetry between the paths to the backplane of each chassis.

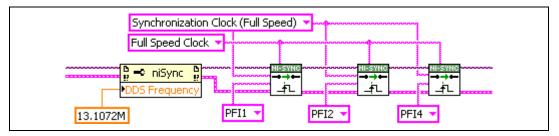

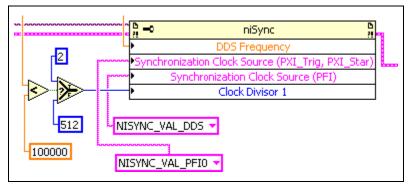

The code snippet shown in Figure 3-7 programs the master NI PXI-665*x* to generate a frequency of 13.1072 MHz, the oversample frequency corresponding to an NI PXI-4472 sampling rate of either 51.2 kS/s or 102.4 kS/s. The code then routes the signal to three front panel pins: PFI 1, PFI 2, and PFI 4. PFI 1 is connected to PFI 0, while PFI 2 and PFI 4 connect to the NI PXI-665*x* modules in the second and third chassis, respectively. *PFI* stands for Programmable Function Interface. These pins are discussed in more detail in the *NI PXI*-665*x User Manual*.

Figure 3-7. Generating and Routing the Oversample Frequency

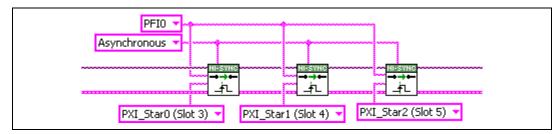

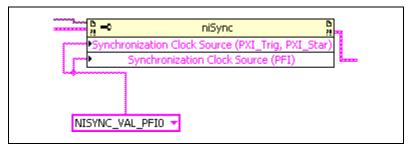

Next, both the master and slave NI PXI-665*x* modules must import the oversample clock signal on PFI 0 and route it to the appropriate PXI star trigger lines. This routing is an asynchronous operation. *Asynchronous routing* means that the signal follows a short path from the PFI input to the PXI star trigger bus and that the NI PXI-665*x* hardware does not actively adjust the phase or timing of the signal. The code shown in Figure 3-8 routes the oversample clock from PFI 0 to NI PXI-4472 boards in Slots 3 through 5.

Figure 3-8. Routing the Oversample Clock Using the PXI Star Trigger Bus

All NI PXI-4472 modules in the system then import this oversample clock from their local PXI star lines. The LabVIEW code snippet used to import the clock is shown in Figure 3-9.

Figure 3-9. Importing the Oversample Clock from PXI\_Star

## Sharing the SYNC Pulse Between Chassis

The SYNC pulse is an active-low signal on PXI\_Trig5 that resets the internal clock dividers in the NI PXI-4472 ADCs and minimizes phase mismatch across devices. When all NI PXI-4472 modules are in a single chassis, NI-DAQ automatically handles the SYNC signal. In a multichassis DSA system; however, you must include code to explicitly handle the SYNC pulse using the NI PXI-665*x*.

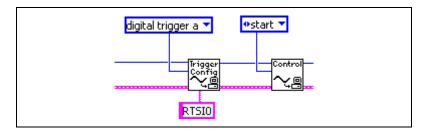

The master NI PXI-665x is responsible for issuing the SYNC. This signal is an active-low pulse, so the NI PXI-4472 ADCs reset when they receive a falling edge on PXI\_Trig5.

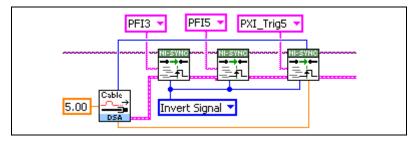

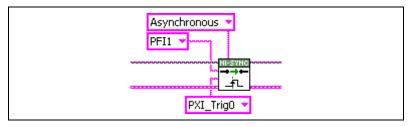

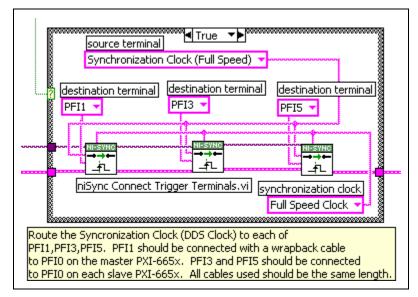

All the generation and routing of the SYNC is performed synchronously with the oversample clock. This synchronous routing means that the edges of the SYNC pulse precisely line up with the edges of the oversample clock. Synchronous routing allows the NI PXI-665*x* in the master chassis to issue the SYNC directly to PXI\_Trig5 without requiring a loopback scheme like that of the oversample clock. Instead, the master NI PXI-665*x* actively delays the pulse based on the cable length between chassis. The code snippet in Figure 3-10 prepares the master to issue the SYNC pulse to PFI3

and PFI5 (physically cabled to PFI 1 on the two slave chassis) and to the local PXI\_Trig5 line. The code includes delay on the master to compensate for propagation delay through 5 m of coaxial cable.

Figure 3-10. Compensating for Propagation Delay on the SYNC Pulse

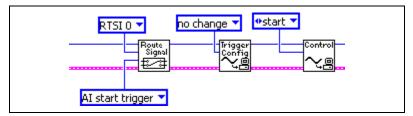

Each slave NI PXI-665*x* then routes the incoming SYNC pulse on PFI1 to the PXI\_Trig5 line as shown in Figure 3-11.

Figure 3-11. Routing the SYNC Pulse

**Note** The previous code snippets illustrate how to set up the routing for the NI PXI-4472 SYNC pulse. They guarantee that when the pulse is generated, it propagates with minimal skew to all the NI PXI-4472 modules in the system. A subsequent subVI that is not shown in the code snippets actually issues the SYNC pulse.

# Sharing the Acquisition Start Trigger Between Chassis

The last signal you must pass between chassis is the start trigger, used to initiate the NI PXI-4472 acquisition. Unlike the oversample clock and the SYNC pulse, the trigger is actually generated by an NI PXI-4472, not by an NI PXI-665*x*. The trigger master (the NI PXI-4472 that generates the trigger signal) can be any NI PXI-4472 residing in the master chassis. As with the single-chassis case, this trigger master can initiate a system

M

acquisition based on an immediate software trigger or an external digital or analog trigger.

The start trigger is passed asynchronously. Asynchronous routing means there is no compensation for cable propagation time between the master and slave chassis. The trigger signal is automatically resynchronized to the sample clock (as opposed to the faster oversample clock) when it is received on each NI PXI-4472 device. For cables shorter than about 30 m, the trigger signal arrives within the same sample interval on both chassis, guaranteeing tight synchronization. However, the trigger signal arrives one sample *later* on the slave chassis for cables longer than about 30 m. There are comments highlighting this effect in the DSA example programs. If you do use long cables, the easiest solution is simply to acquire one more sample on the master chassis than on the slaves and to discard the first sample on the master. This "software data realignment" compensates for the asynchronous trigger delay. If you notice a significant phase mismatch between the same signal acquired on each chassis with long cables, you should try to use the data realignment technique to correct the issue. This behavior generally is easily noticeable if it is present, usually on the order of several degrees. For example, consider the case of a 1 kHz tone acquired at a sampling rate of 100 kS/s. A mismatch of exactly one sample corresponds to a time difference of  $10 \,\mu\text{S}$ , or 1% of a sine tone cycle. Because 360 degrees comprise a full cycle, this error would show up as 3.6 degrees. Note that the trigger delay never produces an error greater than one sample interval. Thus, a 60 or 70 m cable still produces a single sample mismatch, just as would a 30 m cable.

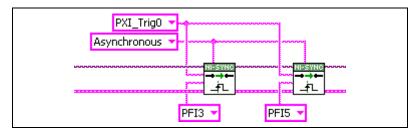

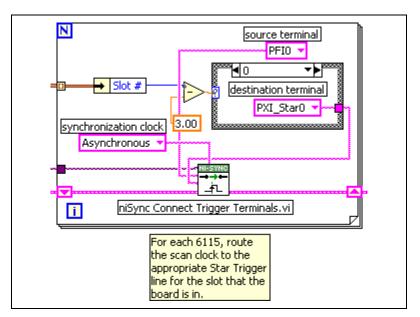

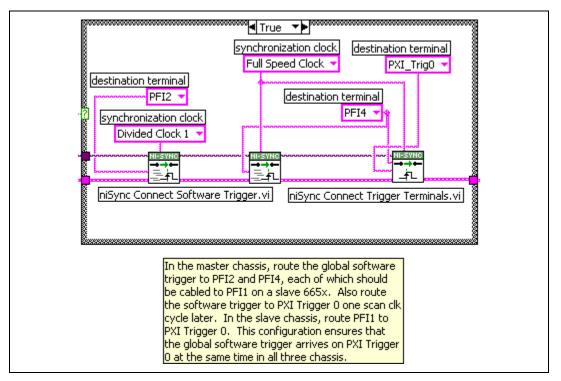

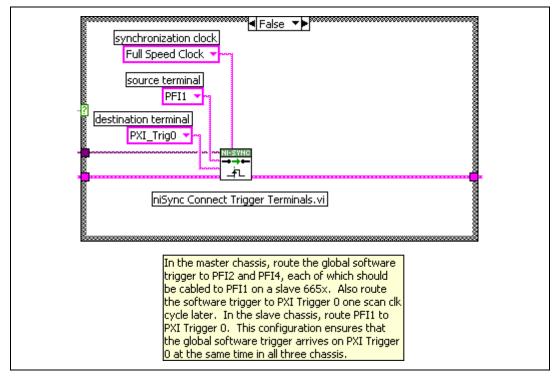

As in the single-chassis case, the trigger master NI PXI-4472 exports the start trigger signal to PXI\_Trig0 (here again, the choice of PXI\_Trig line for passing the trigger is arbitrary). This trigger starts the acquisition on all NI PXI-4472 modules in the master chassis. The NI PXI-665*x* in the master chassis is then responsible for asynchronously routing the start trigger from PXI\_Trig0 to its front panel pins PFI 3 and PFI 5. These same pins were earlier used to propagate the SYNC pulse. Figure 3-12 shows the LabVIEW code snippet used to export the start trigger signal.

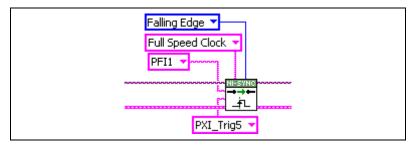

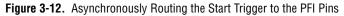

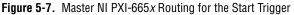

Each slave NI PXI-665*x* then routes the incoming pulse on PFI1 to PXI\_Trig0. Again, this operation is performed asynchronously. Figure 3-13 shows the code snippet you need to route the signal.

Figure 3-13. Routing the Incoming Start Trigger to PXI\_Trig0

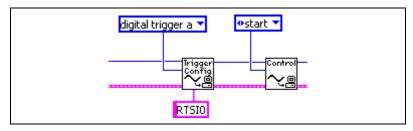

With respect to the acquisition triggering, the NI PXI-4472 modules operate exactly as they do in a single-chassis synchronized system. The slaves digitally trigger from PXI\_Trig0. Figure 3-14 shows the LabVIEW code snippet that you can use to digitally trigger from PXI\_Trig0.

Figure 3-14. Digital Trigger from PXI\_Trig0 on Trigger Slave

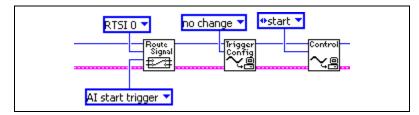

The master exports its start trigger signal to PXI\_Trig0. This operation is shown in Figure 3-15.

In this case, the master starts with an immediate software trigger. However, you could easily modify the parameters for the **AI Trigger Config** VI on the master to enable external digital or analog triggering.

### **Configuring the Chassis**

The following sections provide information for configuring the hardware for four use cases:

- Configuration #1: One Chassis with Synchronized Acquisition and One CPU

- Configuration #2: Two or Three Chassis with Synchronized Acquisition and One CPU

- Configuration #3: Four or More Chassis with Synchronized Acquisition and One CPU

- Configuration #4: Two Chassis with Synchronized Acquisition and Two CPUs

Determine which configuration you will use and refer to that section for more information.

**Note** The following system configurations use 1 m SMB-SMB cables for sharing clock and trigger signals between chassis. You can use longer cables if desired; refer to the *NI PXI-665x User Manual* for the maximum cable length specifications. However, to attain the tightest possible synchronization, it is important that you maintain equal length for all cables in the system and compensate for cable propagation delays in your software.

Software compensation for the SYNC pulse is necessary for all cable lengths. Acquisition start trigger compensation is needed for cables longer than about 30 m. The shipping examples for multichassis DSA systems address cable compensation, and it is also described in the *Using the NI PXI-665x to Route Synchronization Signals Between Multiple Chassis* section.

M

#### Configuration #1: One Chassis with Synchronized Acquisition and One CPU

This configuration allows synchronization between NI PXI-4472 modules housed in a single PXI chassis. The NI PXI-665*x* in PXI Slot 2 provides the oversample clock and SYNC pulse for the modules. Note that a single chassis application does not actually require an NI PXI-665*x*. The same requirements can be fulfilled (with somewhat simpler software) using only NI PXI-4472 modules in a single chassis. These single-chassis examples are included to provide tutorials or "stepping stones" before proceeding to a multichassis system that requires the NI PXI-665*x* and the NI-Sync driver.

The following LabVIEW and LabWindows/CVI example programs are provided for this configuration.

### LabVIEW

- The niSync\_DSA Example Single Chassis VI—This example illustrates a finite acquisition using an NI PXI-665*x* device to synchronize two or more NI PXI-4472 devices in a single chassis. It uses high-level VIs to control the NI PXI-665*x* and NI PXI-4472 modules.

- The niSync\_DSA Example 1 Chassis [Low Level] VI—This example illustrates a finite acquisition synchronizing NI PXI-4472 devices in a single chassis. Unlike the other single-chassis LabVIEW example, this program relies on low-level VIs to control the hardware. This produces a larger and more intricate block diagram. The code is less modular and hierarchical than in the high-level LabVIEW examples.

#### LabWindows/CVI

• Single Chassis Finite Acq—This example illustrates a finite acquisition using an NI PXI-665*x* device to synchronize two or more NI PXI-4472 devices in a single chassis. This program does not include a LabWindows/CVI graphical user interface (GUI), so you can quickly adapt it to work with Microsoft Visual C++ or other ANSI C environments.

#### What You Need to Get Started

To set up and use Configuration #1, you need the following items:

One PXI chassis

CPU

The CPU can be an embedded PXI controller running Windows 2000/XP, or it can be a desktop computer running Windows 2000/XP with an installed remote chassis link (such as MXI-3). The embedded controller or remote link module should be installed in Slot 1 of the chassis.

• One NI PXI-6653 installed in Slot 2 of the PXI chassis

□ Two or more NI PXI-4472 modules. Place the NI PXI-4472 modules in any available PXI slot numbered 3 to 15.

**Note** Do not install the NI PXI-4472 in Slots 16, 17, or 18 of an 18-slot chassis. You cannot route the oversample clock to those slots.

• One 1 m SMB-200 cable

• One 1 kHz sine source (function generator), for testing phase match between chassis.

**Note** The function generator is not required, but it is highly recommended for testing purposes.

#### Connecting the NI PXI-665x Device

Use an SMB-200 cable to connect PFI 0 to PFI 1 on the NI PXI-665*x*. This cable loops back to connect two external pins on the same device.

#### **Connecting the NI PXI-4472 Devices**

Connect the external sine signal to a single input channel on one NI PXI-4472 in each chassis. The same signal should be fed to each chassis to measure the phase mismatch and verify that the synchronization is within specifications.

#### **Configuring and Running the Software Example**

After the hardware has been configured, launch MAX. Verify that all NI PXI-4472 modules are recognized and properly functioning and that the NI PXI-665*x* module is recognized.

$\mathbb{N}$

R

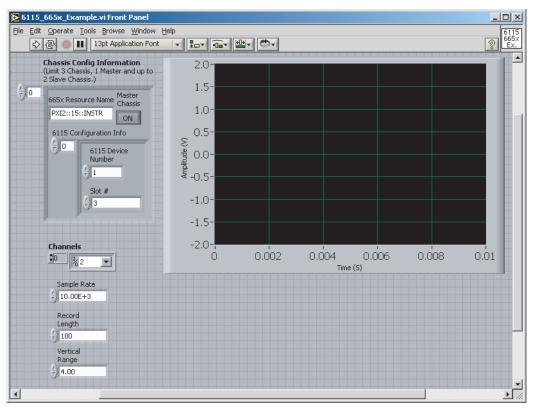

#### Using the niSync\_DSA Example Single Chassis VI

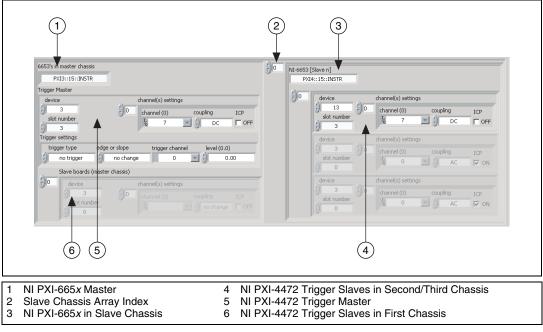

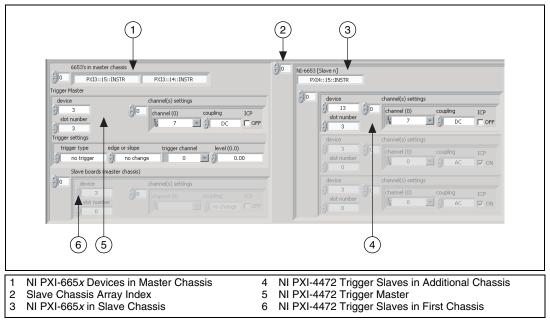

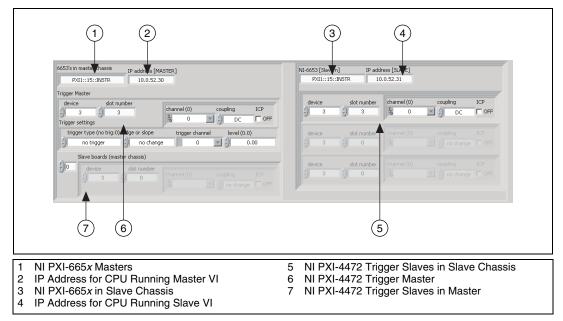

Like the other high-level NI-Sync DSA examples, this program relies on modular subVIs to provide a level of abstraction from the driver calls that directly control the NI PXI-665*x* and NI PXI-4472 devices. All the high-level DSA examples share a nested configuration cluster labeled **Systems Settings**. This is a flexible data structure that allows you to precisely describe your hardware configuration before running the example. Figure 3-16 shows the **System Settings** cluster for the **niSync\_DSA Example Single Chassis** VI.

Figure 3-16. System Settings Cluster for the niSync\_DSA Example Single Chassis VI

• **NI PXI-665x Master**—Enter the VISA Resource Name for the NI PXI-665*x* in the master chassis. The control labeled **6653s in master chassis** is actually an array, although in this particular example the array index control is not shown. The reason for this is that the single-chassis configuration implies only a single NI PXI-665*x* in the system.